Verilog HDL门级建模

创始人

2024-05-20 15:17:18

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者公众号【AIShareLab】,回复 FPGA 也可获取。

基本概念

结构级建模: 就是根据逻辑电路的结构(逻辑图),实例引用Verilog HDL中内置的基本门级元件或者用户定义的元件或其他模块,来描述结构图中的元件以及元件之间的连接关系。

门级建模: Verilog HDL中内置了12个基本门级元件(Primitive,有的翻译为“原语”)模型,引用这些基本门级元件对逻辑图进行描述,也称为门级建模。

基本门级元件(Primitive : 原语)

- 多输入门:and、nand、or、nor、xor、xnor

- 只有单个输出, 1个或多个输入

- 多输出门:not、buf

- 允许有多个输出, 但只有一个输入

- 三态门:bufif0、bufif1、notif0、notif1

- 有一个输出, 一个数据输入和一个控制输入

- 上拉电阻pullup、下拉电阻pulldown

多输入门

多输入门的一般引用格式为:

Gate_ name (OutputA, Input1, Input2,…, InputN);

Gate_ name共6个: and、nand、or、nor、xor、xnor

特点:

- 只有1个输出,

- 有多个输入。

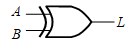

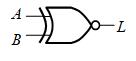

| 原语名称 | 图形符号 | 逻辑表达式 |

|---|---|---|

| and(与门) |  | L = A & B |

| nand(与非门) |  | L = ~(A & B) |

| or(或门) |  | L = A | B |

| nor(或非门) |  | L =~( A | B) |

| xor(异或门) |  | L = A ^ B |

| xnor(同或门) |  | L = A ~^ B |

基本门的调用方法举例:

and A1(out,in1,in2,in3);

xnor NX1(out,in1,in2,in3,in4);

对基本门级元件,调用名A1、NX1可以省略。

若同一个基本门在当前模块中被调用多次,可在一条调用语句中加以说明,中间以逗号相隔。

and、nand真值表

| and | 输入1 | 输入1 | 输入1 | 输入1 | |

|---|---|---|---|---|---|

| 0 | 1 | x | z | ||

| 输入2 | 0 | 0 | 0 | 0 | 0 |

| 输入2 | 1 | 0 | 1 | x | x |

| 输入2 | x | 0 | x | x | x |

| 输入2 | z | 0 | x | x | x |

| nand | 输入1 | 输入1 | 输入1 | 输入1 | |

|---|---|---|---|---|---|

| 0 | 1 | x | z | ||

| 输入2 | 0 | 1 | 1 | 1 | 1 |

| 输入2 | 1 | 1 | 0 | x | x |

| 输入2 | x | 1 | x | x | x |

| 输入2 | z | 1 | x | x | x |

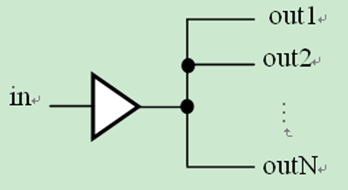

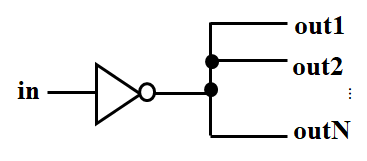

多输出门

允许有多个输出,但只有一个输入。

buf B1(out1,out2,…,in);

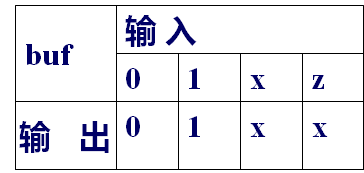

buf真值表

not N1(out1,out2,…,in);

not真值表

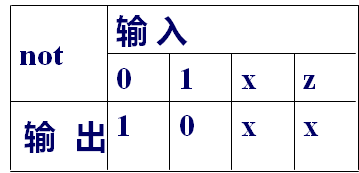

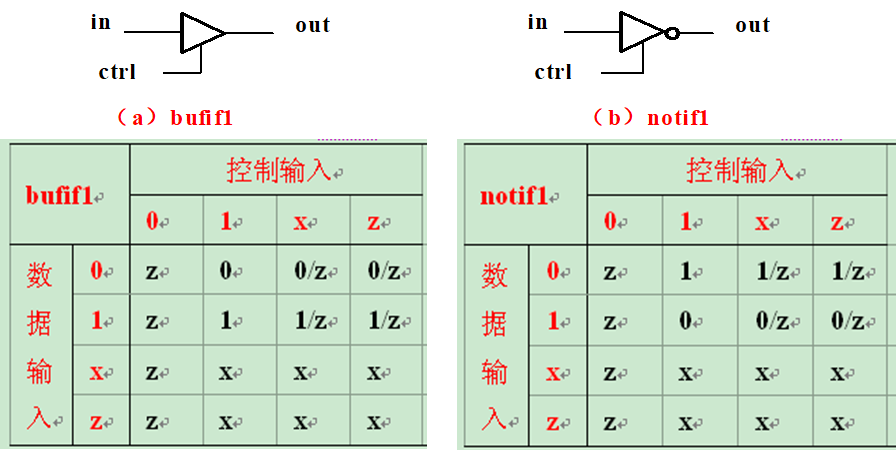

三态门

有一个输出、一个数据输入和一个输入控制。如果输入控制信号无效,则三态门的输出为高阻态z。

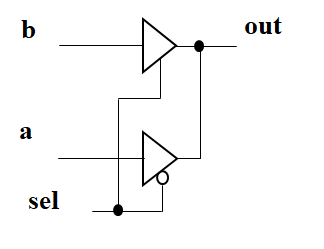

门级建模举例

2选1数据选择器

//Gate-level description

module _2to1muxtri (a,b,sel,out);input a,b,sel;output out;tri out;bufif1 (out,b,sel);bufif0 (out,a,sel);endmodule

小结:门级建模就是列出电路图结构中的元件,并按网表连接 。

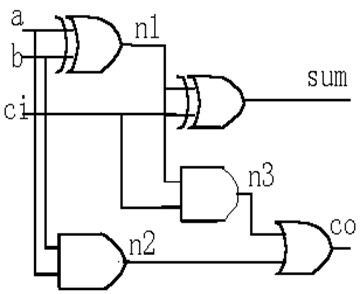

1位全加器

module addbit (a, b, ci, sum, co);

input a, b, ci;

output sum, co;

wire a, b, ci, sum, co, n1, n2, n3; xor u0(n1, a, b), u1(sum, n1, ci); and u2(n2, a, b), u3(n3, n1, ci); or (co, n2, n3); endmodule

若同一个基本门在当前模块中被调用多次,可在一条调用语句中加以说明,中间以逗号相隔。

门级描述小结

- 给电路图中的每个输入输出引脚赋以端口名。

- 给电路图中每条内部连线 取上各自的连线名。

- 给电路图中的每个逻辑元件取一个编号 (即“调用名”)。

- 给所要描述的这个电路模块确定一个模块名。

- 用module定义相应模块名的结构描述,并将逻辑图中所有的输入输出端口名列入端口名表项中,再完成对各端口的输入输出类型说明。

- 依照电路图中的连接关系,确定各单元之间端口信号的连接,完成对电路图内部的结构描述。

- 最后用endmodule结束模块描述全过程。

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

欢迎公众号【AIShareLab】,一起交流更多相关知识,前沿算法,Paper解读,项目源码,面经总结。

上一篇:我应该是懂居家办公的吧?

相关内容

热门资讯

怎么样的桃花 桃花近看远看的样...

今年的“三八”妇女节,阳光明媚,踏青赏花正当时。遂与姐妹们共赴十里蓝山,与花海来一场春天的约会。十里...

苗族的传统节日 贵州苗族节日有...

【岜沙苗族芦笙节】岜沙,苗语叫“分送”,距从江县城7.5公里,是世界上最崇拜树木并以树为神的枪手部落...

北京的名胜古迹 北京最著名的景...

北京从元代开始,逐渐走上帝国首都的道路,先是成为大辽朝五大首都之一的南京城,随着金灭辽,金代从海陵王...

应用未安装解决办法 平板应用未...

---IT小技术,每天Get一个小技能!一、前言描述苹果IPad2居然不能安装怎么办?与此IPad不...

脚上的穴位图 脚面经络图对应的...

人体穴位作用图解大全更清晰直观的标注了各个人体穴位的作用,包括头部穴位图、胸部穴位图、背部穴位图、胳...

长白山自助游攻略 吉林长白山游...

昨天介绍了西坡的景点详细请看链接:一个人的旅行,据说能看到长白山天池全凭运气,您的运气如何?今日介绍...

猫咪吃了塑料袋怎么办 猫咪误食...

你知道吗?塑料袋放久了会长猫哦!要说猫咪对塑料袋的喜爱程度完完全全可以媲美纸箱家里只要一有塑料袋的响...

demo什么意思 demo版本...

618快到了,各位的小金库大概也在准备开闸放水了吧。没有小金库的,也该向老婆撒娇卖萌服个软了,一切只...

世界上最漂亮的人 世界上最漂亮...

此前在某网上,选出了全球265万颜值姣好的女性。从这些数量庞大的女性群体中,人们投票选出了心目中最美...

苗族的传统节日 贵州苗族节日有...

【岜沙苗族芦笙节】岜沙,苗语叫“分送”,距从江县城7.5公里,是世界上最崇拜树木并以树为神的枪手部落...

北京的名胜古迹 北京最著名的景...

北京从元代开始,逐渐走上帝国首都的道路,先是成为大辽朝五大首都之一的南京城,随着金灭辽,金代从海陵王...

怎么样的桃花 桃花近看远看的样...

今年的“三八”妇女节,阳光明媚,踏青赏花正当时。遂与姐妹们共赴十里蓝山,与花海来一场春天的约会。十里...

长白山自助游攻略 吉林长白山游...

昨天介绍了西坡的景点详细请看链接:一个人的旅行,据说能看到长白山天池全凭运气,您的运气如何?今日介绍...

应用未安装解决办法 平板应用未...

---IT小技术,每天Get一个小技能!一、前言描述苹果IPad2居然不能安装怎么办?与此IPad不...

脚上的穴位图 脚面经络图对应的...

人体穴位作用图解大全更清晰直观的标注了各个人体穴位的作用,包括头部穴位图、胸部穴位图、背部穴位图、胳...

世界上最漂亮的人 世界上最漂亮...

此前在某网上,选出了全球265万颜值姣好的女性。从这些数量庞大的女性群体中,人们投票选出了心目中最美...

demo什么意思 demo版本...

618快到了,各位的小金库大概也在准备开闸放水了吧。没有小金库的,也该向老婆撒娇卖萌服个软了,一切只...

猫咪吃了塑料袋怎么办 猫咪误食...

你知道吗?塑料袋放久了会长猫哦!要说猫咪对塑料袋的喜爱程度完完全全可以媲美纸箱家里只要一有塑料袋的响...