AXI-Stream 学习笔记

参考

https://wuzhikai.blog.csdn.net/article/details/121326701

https://zhuanlan.zhihu.com/p/152283168

AXI4 介绍

AXI4 是ARM公司提出的一种片内总线,描述了主从设备之间的数据传输方式。主要有AXI4_LITE、AXI4_FULL、AXI4_STREAM三种。

- AXI4_LITE:不支持突发传输,一般用于小数据量的IP初始化和嵌入式设备数据传输。

- AXI4_FULL:可称为AXI4,支持突发传输,突发长度为1~256。

- AXI4_STREAM:流数据,丢弃了地址项,用于高速数据传输。

AXI-Stream顾名思义是用来传输数据流的,如图像输入,高速AD等,这种数据流的处理一般是和DMA一并使用的。

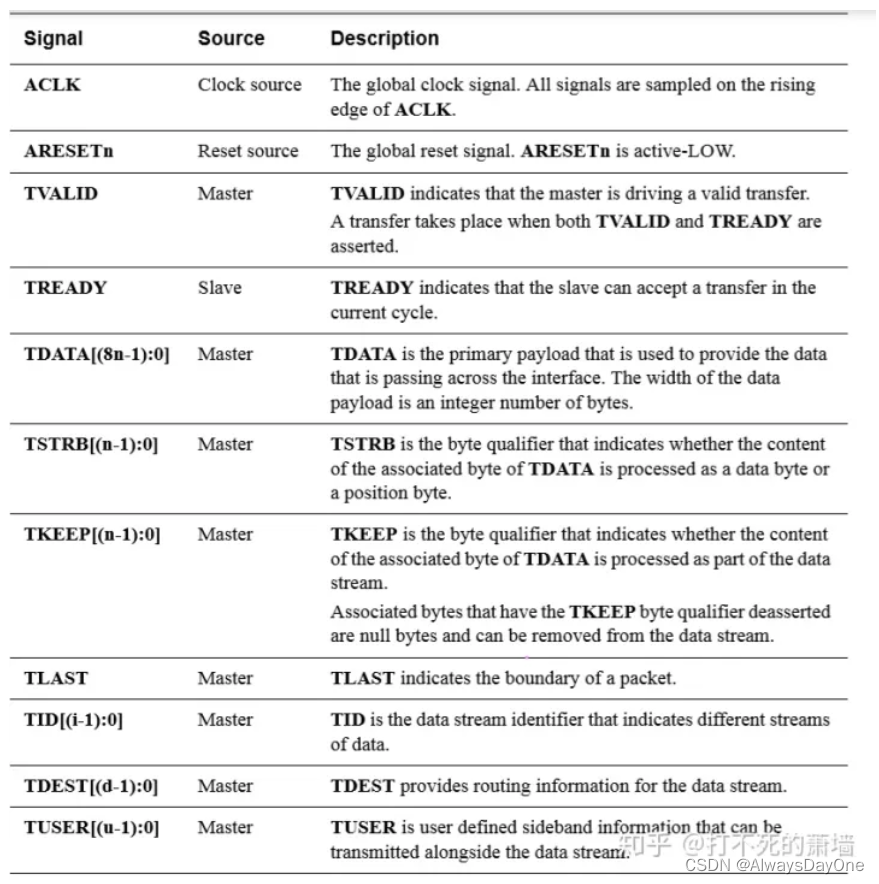

AXI-Stream 接口

全局信号

ACLK和ARESETn信号,不必多说,时钟和复位信号

握手信号

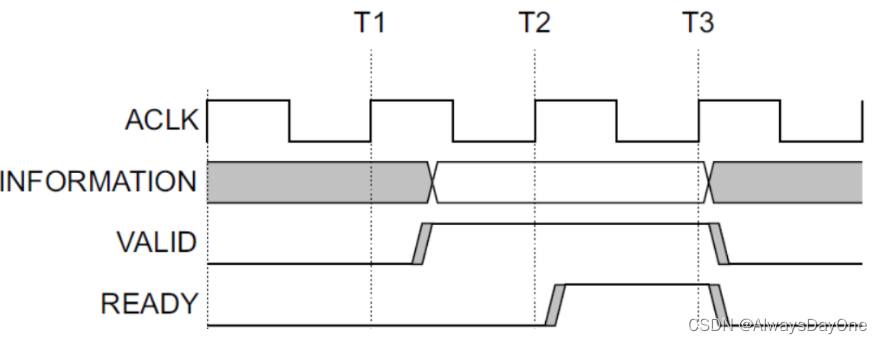

TVALID和TREADY是握手信号,TVALID从master发到slave,TREADY反之。

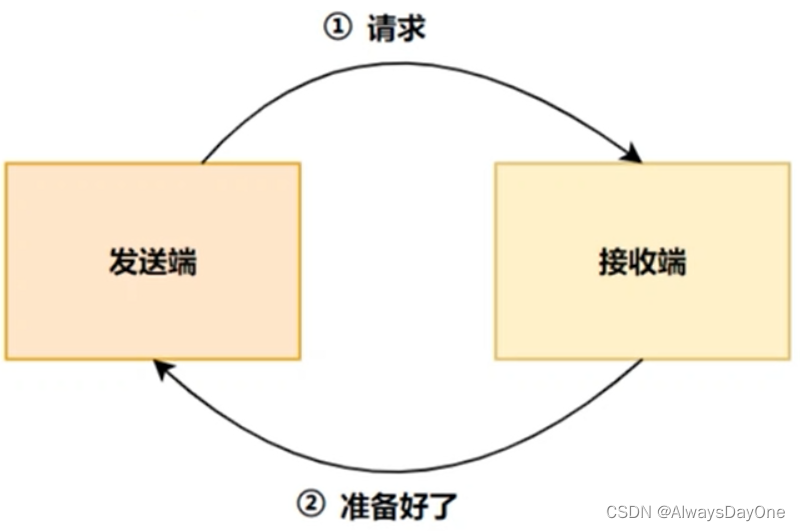

使用VALID和READY信号作为控制信号来传输数据,只有VALID与READY同时为高的时候,才可以正常的发送数据,而通常情况下,VALID信号用来表示什么时候 主设备 “地址、数据、和控制信号”是有效的,而READY信号则用来表示什么时候 从设备 准备好采集数据了。

- VALID:发送端准备好了数据,开始请求接收端接收

- READY:接收端准备好了,可以接收发送端的数据

- INFOMATION:表示发送端请求所携带的数据,最终将传输到接收端

对于这三个信号,会存在以下三种情况:

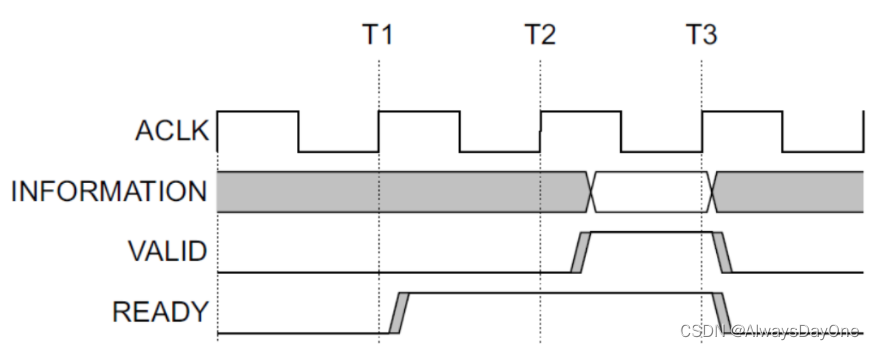

- READY 信号先于VALID 信号高电平:T2 时刻READY 信号的拉高,代表从设备准备好采样了,但T2 时刻,VALID 未拉高,因此未进行采样,而T3 时刻,VALID 拉高了,完成握手,数据传输。

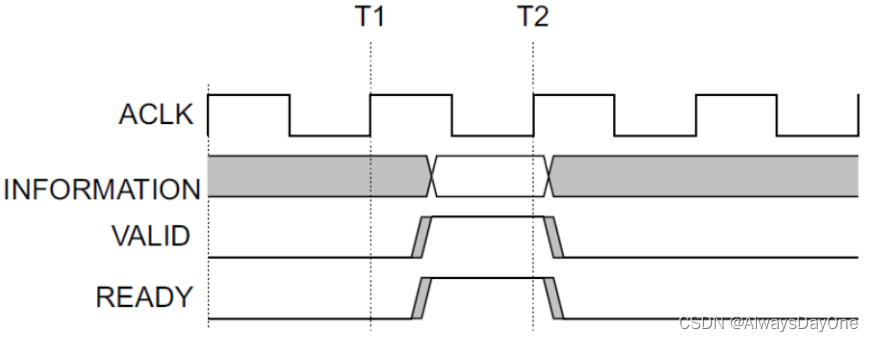

- VALID 和READY 信号在T2 时刻同时为高电平:数据有效的同时也可以进行采样,在T2 时刻的上升沿,采样到正确数据,握手正确,再往后二者都拉低,数据进行了正确传输。

- READY 信号晚于VALID 信号高电平:表明数据先正确,然后READY拉高表明可以进行采样,T3时刻进行了采样,完成握手,再往后二者信号都拉低,数据传输。

此外,协议规定,“VALID 信号一旦拉高,除非READY 信号拉高接收数据完成,不会主动变低”。

总结:只要主从机之间发生数据传输,就会发生“握手”过程。

数据流

TDATA代表数据流。主机发送给从机的信息(数据,空数据,位置数据),为BYTE的整数倍,是AXIS传输通道的主要载荷。

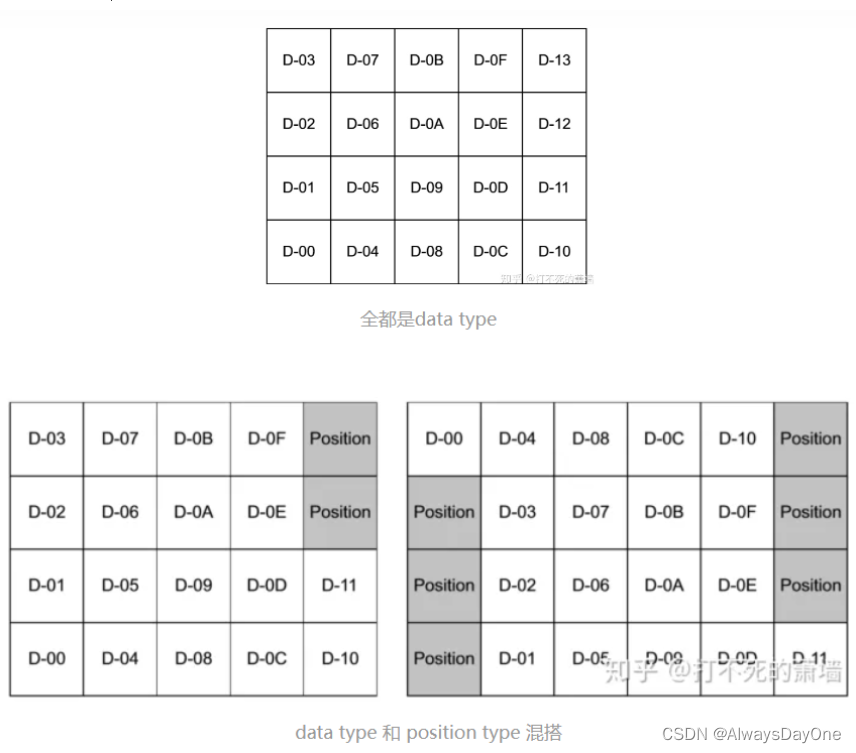

AXI4-Stream传输的数据流包含三种类型:data byte、position byte、null byte。

data byte是最有意义的数据;position byte作为占位符使用,可以用来表征date type 的相对位置,null byte不包含任何有用的信息。

数据流的结构可以有很多种:

- 仅data byte,不包含position byte和null byte

- data byte和 null byte混着传输

- position byte和 data byte混着传输

- 三者都混着传输

数据流修饰

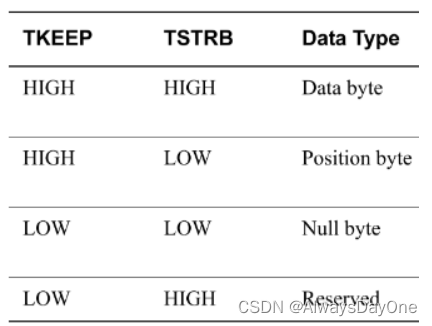

TKEEP和TSTRB用于对数据流进行修饰,表示当前数据包中每个字节的数据流类型(即data byte、position byte、null byte)。

如总线上数据的字节数为n,如接口表中有TDATA[(8*n-1):0],TKEEP[n-1:0],TSTRB[n-1:0],TKEEP和TSTRB的每一位对应修饰一个字节的数据,其关系如下表

如n = 4,TDATA = 0x0000FFFF,TKEEP = 2’b0011,TSTRB= 2’b0001。由于TKEEP和TSTRB高2位为0,那么TDATA的高阶2字节为null byte;由于TKEEP和TSTRB低2位为01,那么TDATA的低阶2字节为Position byte和data byte。

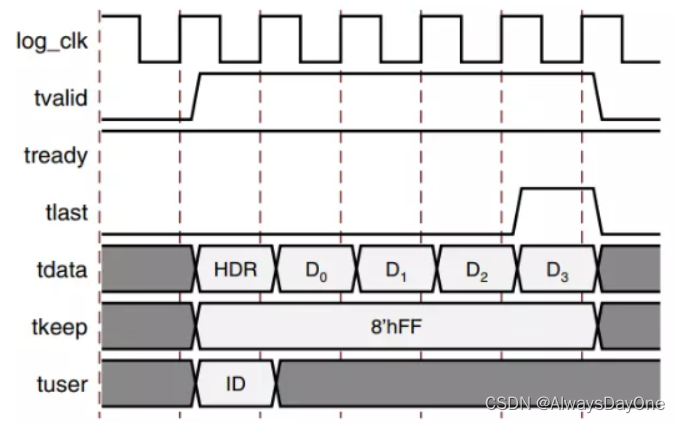

TLAST

在具有帧或者包概念的流式传输中,TLAST信号,用来表示一个包的结尾。例如发送大小为5字节的包,每次1字节,在发送第5个字节的时候,可以把TLAST信号拉高,来表示这个包发送完了。时序如下:

对于没有包或帧概念的数据流,TLAST的默认值是不确定的。则有以下选项:

- 设置TLAST低。这表明所有传输都在同一个数据包中

- 设置TLAST高。这表明所有传输都是单独的数据包

- 自动产生脉冲TLAST值。这个选项在固定数量的传输之后断言TLAST,例如在两次或16次传输之后

传输修饰类

这三个信号通常是在多个AXI接口的组件构成拓扑结构时用于表征传输的源与目的:

- TID :表示不同数据流的数据流标识符,指示数据来源

- DEST :用于提供路由信息,指示数据目的地

- TUSER:AXI4协议留给用户自定义的数据,可用来表征额外的信息

总结

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有地址接口,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。