xilinx GTX 时钟详解

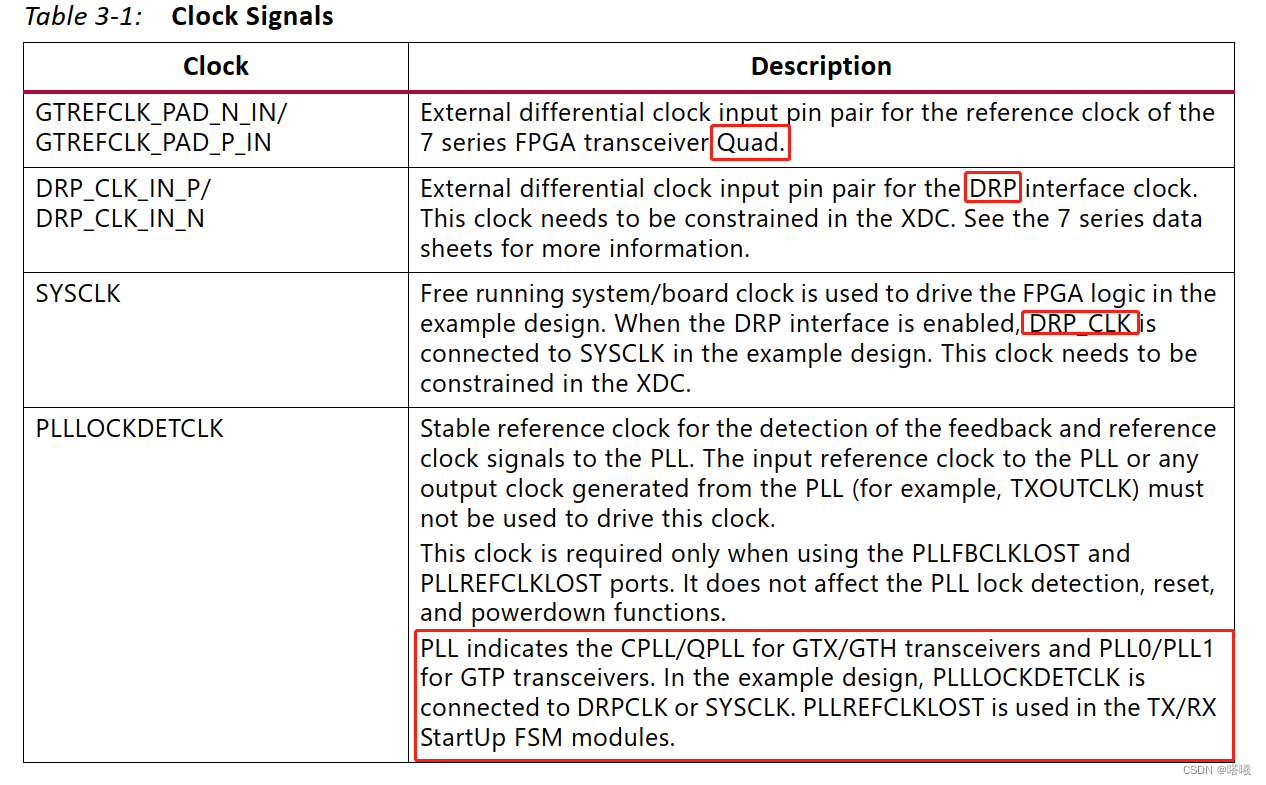

一、用户接口信号的时钟(GTREFCLK_PAD_N_IN、DRP_CLK_IN_P、SYSCLK、PLLLOCKDETCLK)

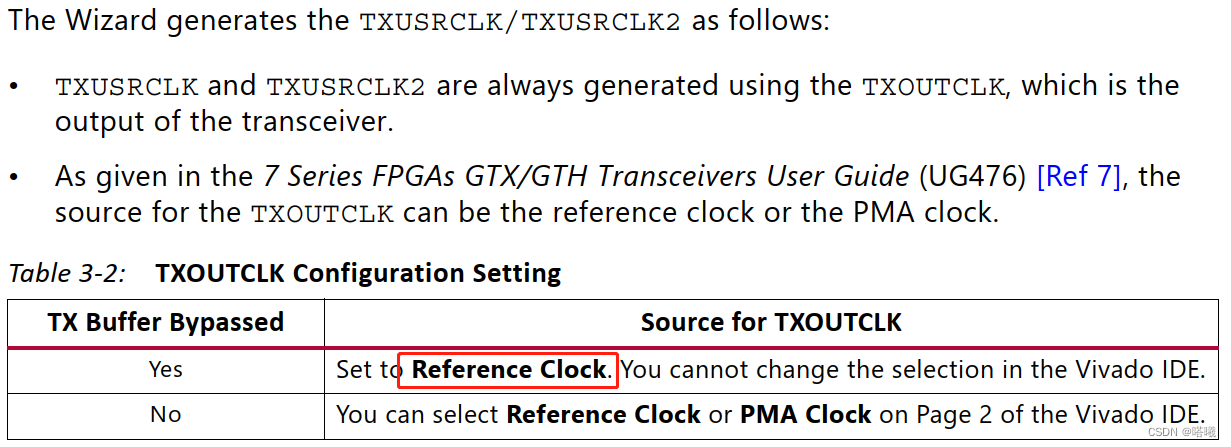

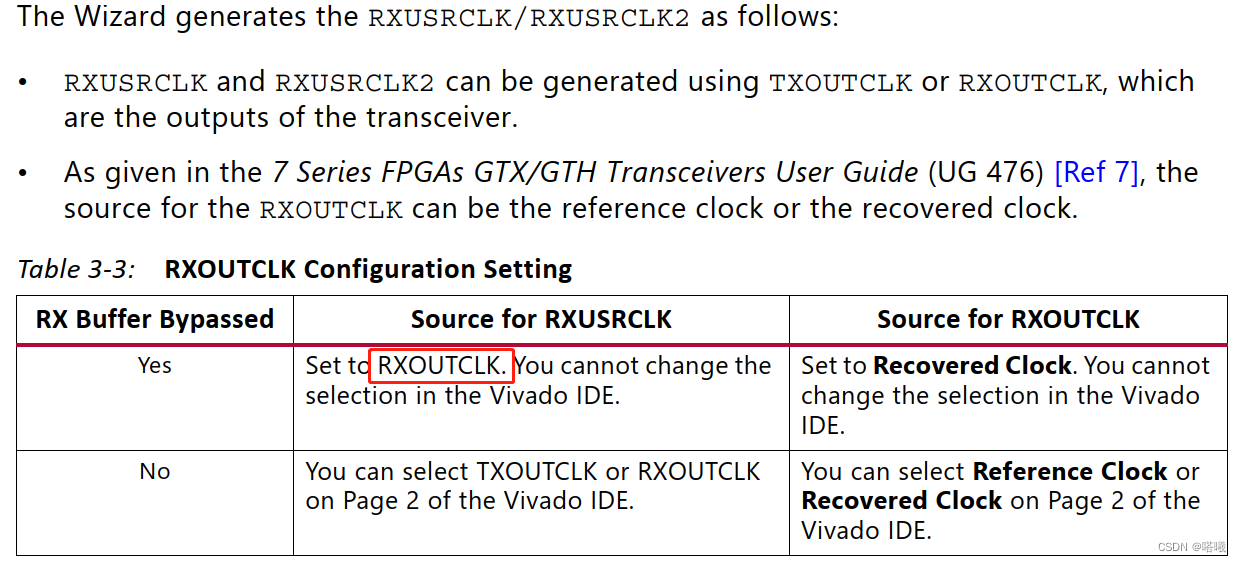

二、TX/RXUSRCLK and TX/RXUSRCLK2、TXOUTCLK

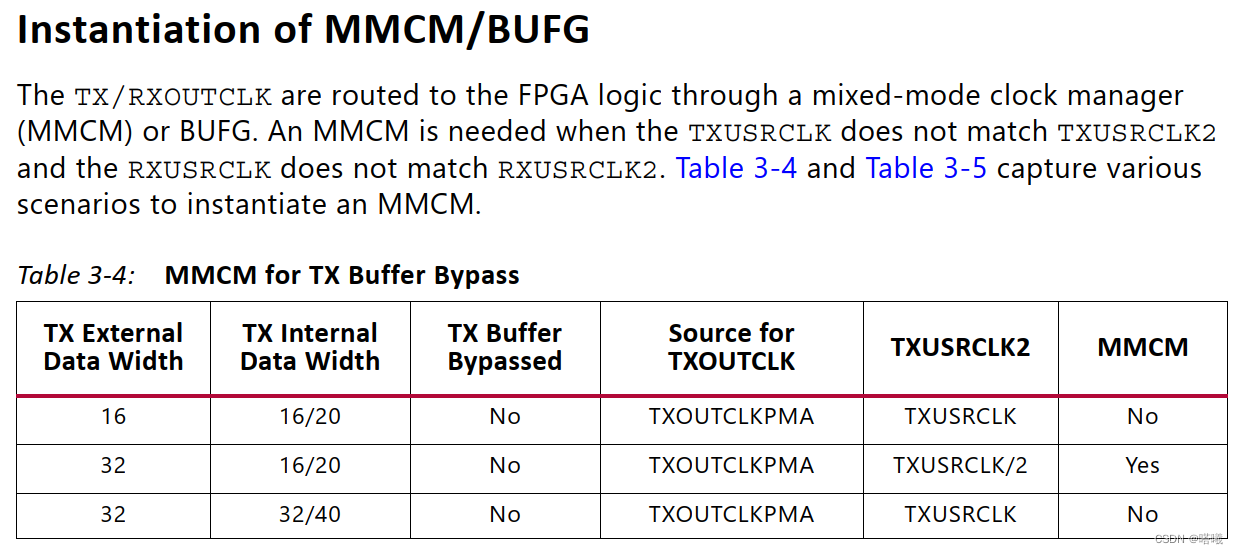

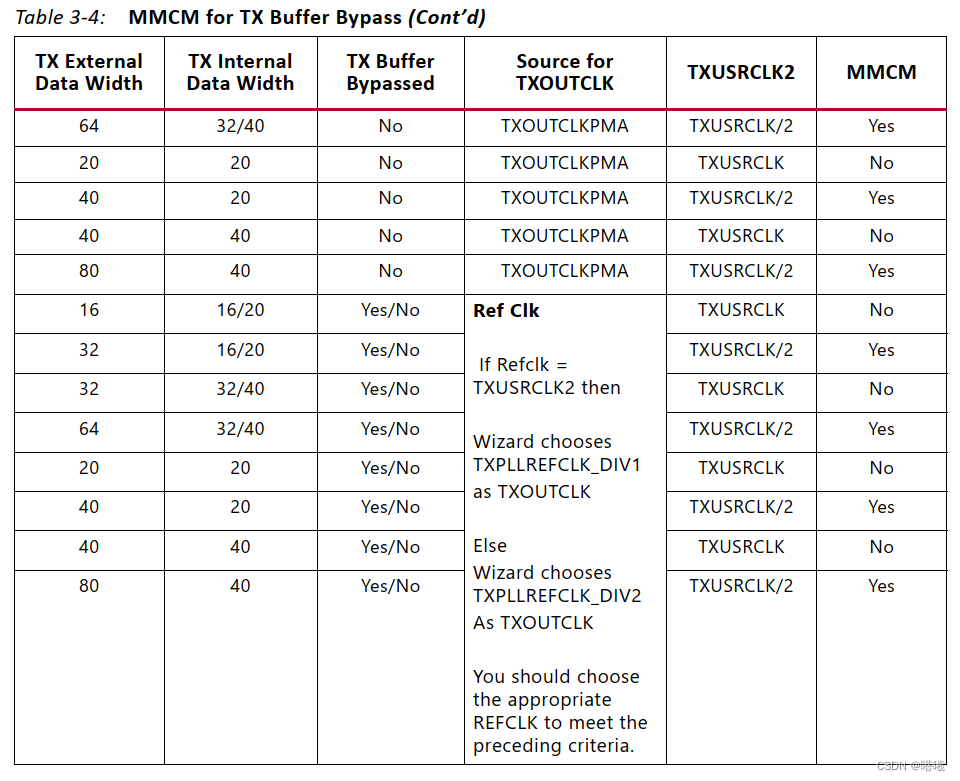

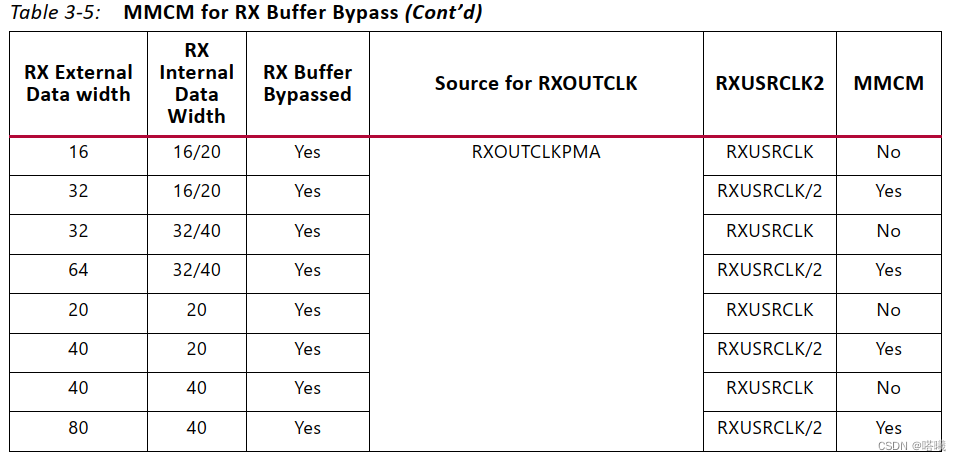

三、mmcm时钟(两个用户时钟不匹配,以及分不出来速率,需要启用)

专业俗语:

TX External Data Width:外部宽度大,时钟大而慢。TXOUTCLK这个时钟。

TX Internal Data Width:内部宽度小,时钟小而快。TXUSRCLK2这个时钟。

TX Buffer Bypassed: 缓存fifo(PMA、PCS之间,特别启用编码变速箱)

Source for TXOUTCLK:启用旁路,则只能使用参考时钟

TXUSRCLK:外部宽度,其实就是真实用户时钟。

TXUSRCLK2:内部宽度,其实就是真实GT口接受之后处理部分。

MMCM:TXUSRCLK、TXUSRCLK2不匹配会启用,或者速率很难计算出来

TXOUTCLKPMA:如果启用TX Buffer Bypassed,Source for TXOUTCLK不能选择这个,只能选择参考时钟。

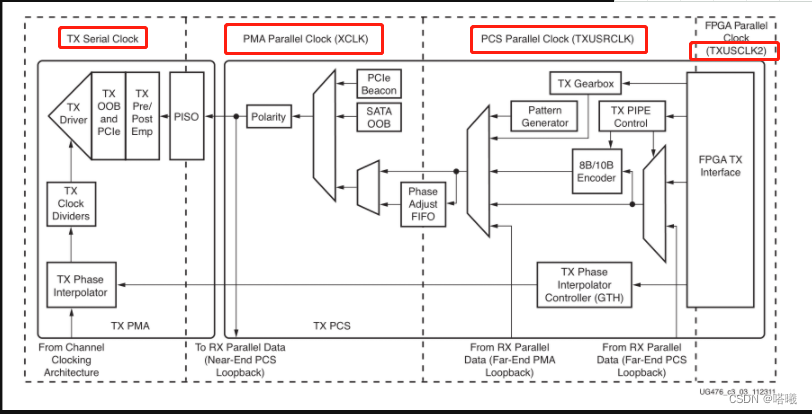

四、内部结构分布时钟

TX Serial Clock:真实速率时钟

PMA、PCS(txusrclk):并行时钟

TX buffer的作用(缓存FIFO,特别编码使用变速箱,如果使用变速箱、可能PMA、PCS时钟不一致)

GTX/GTH收发器的TX数据通路有两个用于PCS的内部并行时钟域:PMA并行时钟域(XCLK)和TXUSRCLK域。为了传输数据,XCLK速率必须与TXUSRCLK速率相匹配,并且必须解决两个域之间的所有相位差。

GTX/GTH Transmitter包括一个TX缓冲器和一个TX相位校准电路,以解决XCLK和TXUSRCLK域之间的相位差异。当TX buffer被旁路时,TX相位校正电路(phase alignment)被使用。所有的TX数据路径必须使用TX缓冲器或TX相位对准电路。

##2.选择收发器的位置和时钟。

Line Rate: 设置为所需的目标线路速率,以Gb / s为单位.

Reference clock: 从列表中选择应用程序要提供的最佳参考时钟频率。

Tx off: 选择此选项将禁用收发器的TX路径。收发器仅充当接收器。

##3.允许您选择编码和8B / 10B可选端口

TX

External Data Width:应用程序传来的数据位数

Encoding:发送前可选择编码

Internal Data Width:内部数据位数

RX

External Data Width:应用程序传来的数据位数

Encoding:发送前可选择解码

Internal Data Width:内部数据位数

Use DRP:选择此选项可将CHANNEL块的动态重配置端口信号提供给应用程序

下面一堆选项具体配置可看图。有关编码的一些选项,如果传送信息没有特数字符不用太管。

Enable TX Buffer:使能发送缓冲区,低时延可绕过发送缓冲区

TX Buffer Bypass Mode:绕行缓冲区的模式,如果想要具体了解可参考UG476

Enable RX Buffer:使能接收缓冲区。

RX Buffer Bypass Mode:绕行缓冲区模式。

RXTXOUTCLK:RX/TXUSRCLK由RX/TXOUTCLK驱动。RX buffer is bypassed, RXOUTCLK不可用。

RX/TXPLLREFCLK:选中,RX/TXOUTCLK由参考时钟生成,否则选择合适的RX/TXOUTCLK

上一篇:nodejs的简单复习