闪存系统性能优化方向?NAND Cache Read(闪存缓冲读) 原理与实战?

Hello 大家好, 我是元存储~

目录

前言

1. 提升效果

2. Cache Read 是什么?

3. Cache Read 的闪存基础

4. Cache Read 原理

5. Cache Read 命令和时序

5.1 READ PAGE CACHE SEQUENTIAL (31h)

5.2 READ PAGE CACHE RANDOM (00h-31h)

6. Cache Read 用处

参考

前言

NAND Flash凭借其高性能、以及低成本等特性大受欢迎,是最为广泛的非易失存储介质。为了满足业务性能要求,人们想了许多方法来提升基于NAND Flash的系统性能, 本节我们带大家探索一下其中从Cache Read 是如何提升性能, 提升大不大?

1. 提升效果

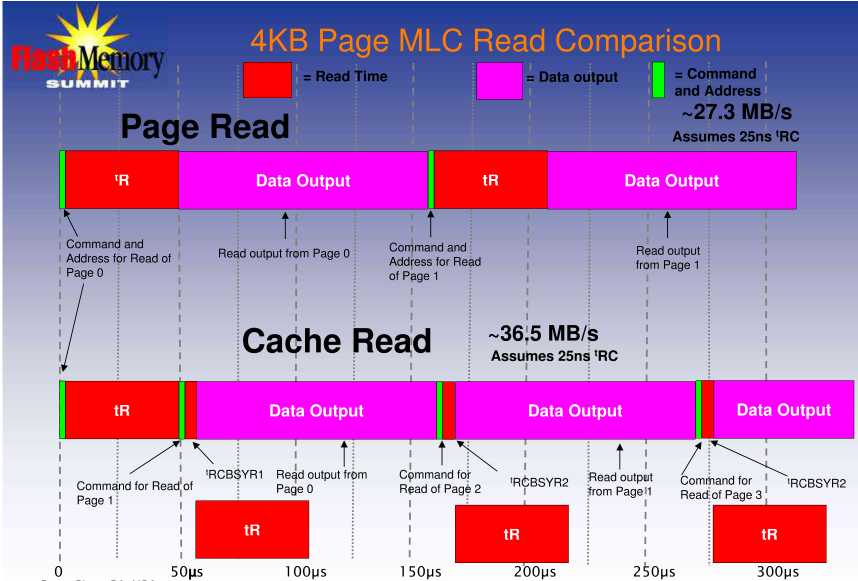

话不多说, 先看提升效果。Cache Read 相对于简单的 Page Read ,吞吐率从 27.3MB/s 提升到 36.5MB/s, 提升了 33%.

觉得还蛮给力的就继续往下探索吧?

2. Cache Read 是什么?

在onfi接口标准(在http://www.onfi.org/~/media/onfi/specs/onfi_4_0-gold.pdf?la=en可获得)中定义了“readcache”系列命令,包括“readcachesequential”与“readcacherandom”。toggle接口标准中定义了类似的“sequentialcacheread”与“randomcacheread”命令。

而page register起到缓冲的作用,在读多个page时,当cache传输一个page数据时,page register提前把下一个page的数据准备好。[3]

存储控制器向nand闪存芯片发出的“cacheread”命令,指示nand芯片从页寄存器读出一个数据页的同时,在相同的lun(logicunit,逻辑单元)上从闪存单元阵列中读出另一页数据。

主流的nand闪存芯片都支持“cacheread”的命令。

这里的Cache Read 是从nand 芯片中的闪存颗粒阵列里,读到NAND 芯片中的 Cache Register. 而不是指的电脑或者 SSD 带的Cache。那个属于Cache 缓存, 不再此讨论。

3. Cache Read 的闪存基础

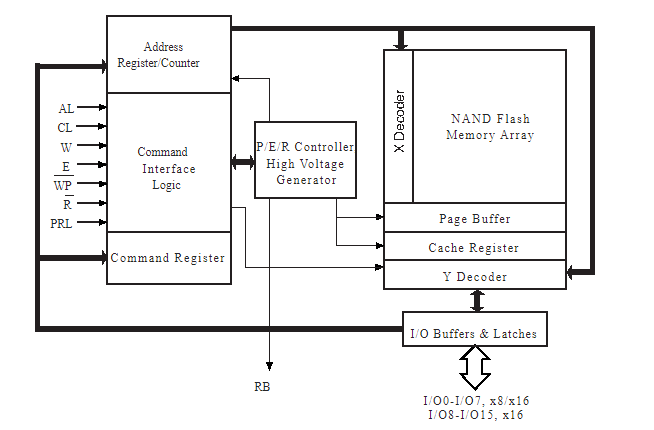

NAND 里每个Plane 自带有Cache Reister 和 Page Buffer, 每个的大小都是一个page(页) 的大小, 常见是 16KB(Main Area) + 2KB(Spare Area)。这为Cache Read 提供了可能。

4. Cache Read 原理

在当前页从缓存寄存器输出时,将block内的下一页数据读取到数据寄存器中(注意这里有数据寄存器,数据寄存器和缓存寄存器不是一个东西)。

5. Cache Read 命令和时序

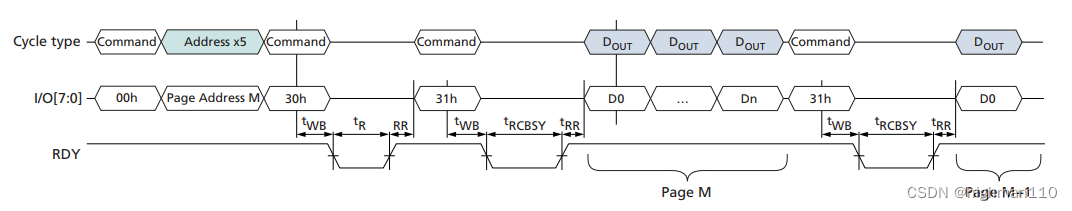

5.1 READ PAGE CACHE SEQUENTIAL (31h)

READ PAGE CACHE SEQUENTIAL (31h):在当前页从缓存寄存器输出时,将block内的下一页数据读取到数据寄存器中。此命令当裸片(LUN)准备就绪(RDY=1,ARDY=1)时,该命令可以被接受。在读取页面缓存(31h,00h-31h)操作(RDY=1和ARDY=0)期间,该命令也可以被接受。

将31h写入命令寄存器,发出此命令后,R/B#变为低电平,裸片(LUN)在tRCBSY时间内处于繁忙状态(RDY=0,ARDY=0)。tRCBSY之后,R/B#变为高,裸片(LUN)忙于缓存操作(RDY=1,ARDY=0),这表明缓存寄存器可用,并且指定的页正在从NAND闪存阵列复制到数据寄存器。此时,数据可以从缓存寄存器的列地址0开始输出。随机数据读取(05h-E0h)命令可以用于更改从缓存寄存器输出的数据的列地址。

READ PAGE CACHE SEQUENTIAL(31h)命令可用于跨越block边界。如果在当前block的最后一页读入数据寄存器之后发出读取页缓存序列(31h)命令,则读取的下一页将是下一个逻辑block中的page。如果是跨die读取,则此命令无法实现,应使用READ PAGE CACHE LAST(3Fh)命令。PAGE CACHE SEQUENTIAL 要求要读的下一个page 是连续的[2]

如下为顺序读缓存页时序图:

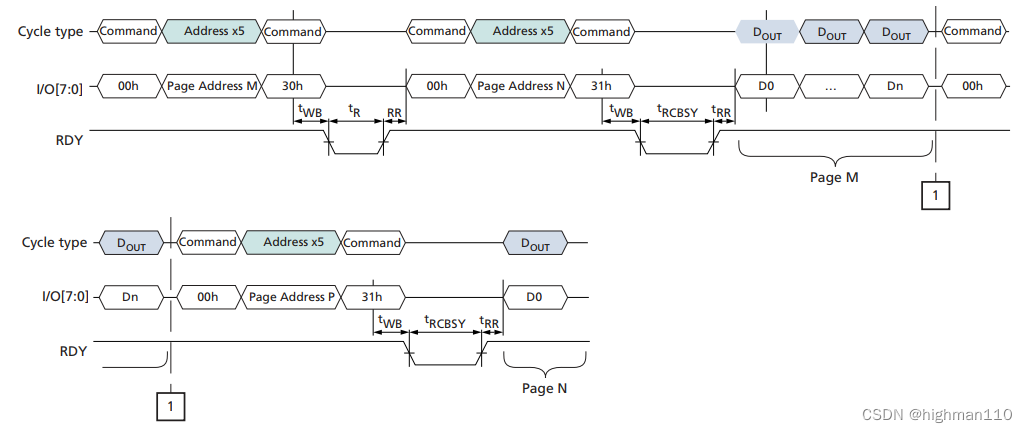

5.2 READ PAGE CACHE RANDOM (00h-31h)

READ PAGE CACHE RANDOM (00h-31h):此命令将指定的块中的页读入数据寄存器,同时从缓存寄存器输出前一页。当die(LUN)准备就绪(RDY=1,ARDY=1)时,该命令被接受。在读取页面缓存(31h,00h-31h)操作(RDY=1和ARDY=0)期间,它也可以被(LUN)接受。

要发出此命令,需将00h写入命令寄存器,然后将n个地址周期写入地址寄存器,最后将31h写入指令寄存器。指定地址中的列地址将被忽略。裸片(LUN)地址必须与先前的READ PAGE(00h-30h)命令或先前的READPAGE CACHE RANDOM(00h-31h)命令(如果适用)匹配。

发出此命令后,R/B#变为低电平,在tRCBSY时间段内,die(LUN)处于繁忙状态(RDY=0,ARDY=0)。tRCBSY之后,R/B#变为高,die(LUN)忙于缓存操作(RDY=1,ARDY=0),这表明缓存寄存器可用,并且指定的页正在从NAND闪存阵列复制到数据寄存器。此时,数据可以从缓存寄存器的列地址0开始输出。随机数据读取(05h-E0h)命令可以用于更改从缓存寄存器输出的数据的列地址。[2]

如下为随机读缓存页时序图:

6. Cache Read 用处

Sequential Cache Read 可用于对闪存芯片进行顺序读过程中, 可显著提高顺序读的速度。如果是随机读, 一般用Cache Read 增加了复杂度, 效果还不大。Random Cache Read 有点鸡肋,使用较少。

参考

[1] 实现快速读取的方法及介质接口控制器与流程,

https://www.xjishu.com/zhuanli/55/201710499881.html

[2] 【FLASH存储器系列十二】Nand Flash芯片使用指导之二-CSDN博客

[3] 04_nand基本操作_Chockong的博客-CSDN博客

上一篇:关于复杂链表的复制问题(力扣)

下一篇:多线程开发